YOUTUBE 頻道 HIGH YIELD 最近推出影片 The definitive Intel Arrow Lake deep-dive (來源),利用 DIE SHOT 圖片介紹 ARROW LAKE-S (CORE ULTRA 200S) 各 TILE 的細節。他經研究分析更發現 INTEL 藏有更多 PCIe 通道未有利用,令筆者感到萬分震驚。要是 INTEL 完全利用這些通道,豈不遠遠拋離 AMD,AMD 串連三顆 PROM21 B650 都追不上了滿血的 CORE ULTRA 200S + Z890 平台擴展性。

YOUTUBE 頻道 HIGH YIELD 最近推出影片 The definitive Intel Arrow Lake deep-dive (來源),利用 DIE SHOT 圖片介紹 ARROW LAKE-S (CORE ULTRA 200S) 各 TILE 的細節。他經研究分析更發現 INTEL 藏有更多 PCIe 通道未有利用,令筆者感到萬分震驚。要是 INTEL 完全利用這些通道,豈不遠遠拋離 AMD,AMD 串連三顆 PROM21 B650 都追不上了滿血的 CORE ULTRA 200S + Z890 平台擴展性。

所以到底為什麼 ARROW LAKE-S GEN5 SSD 跑不滿?

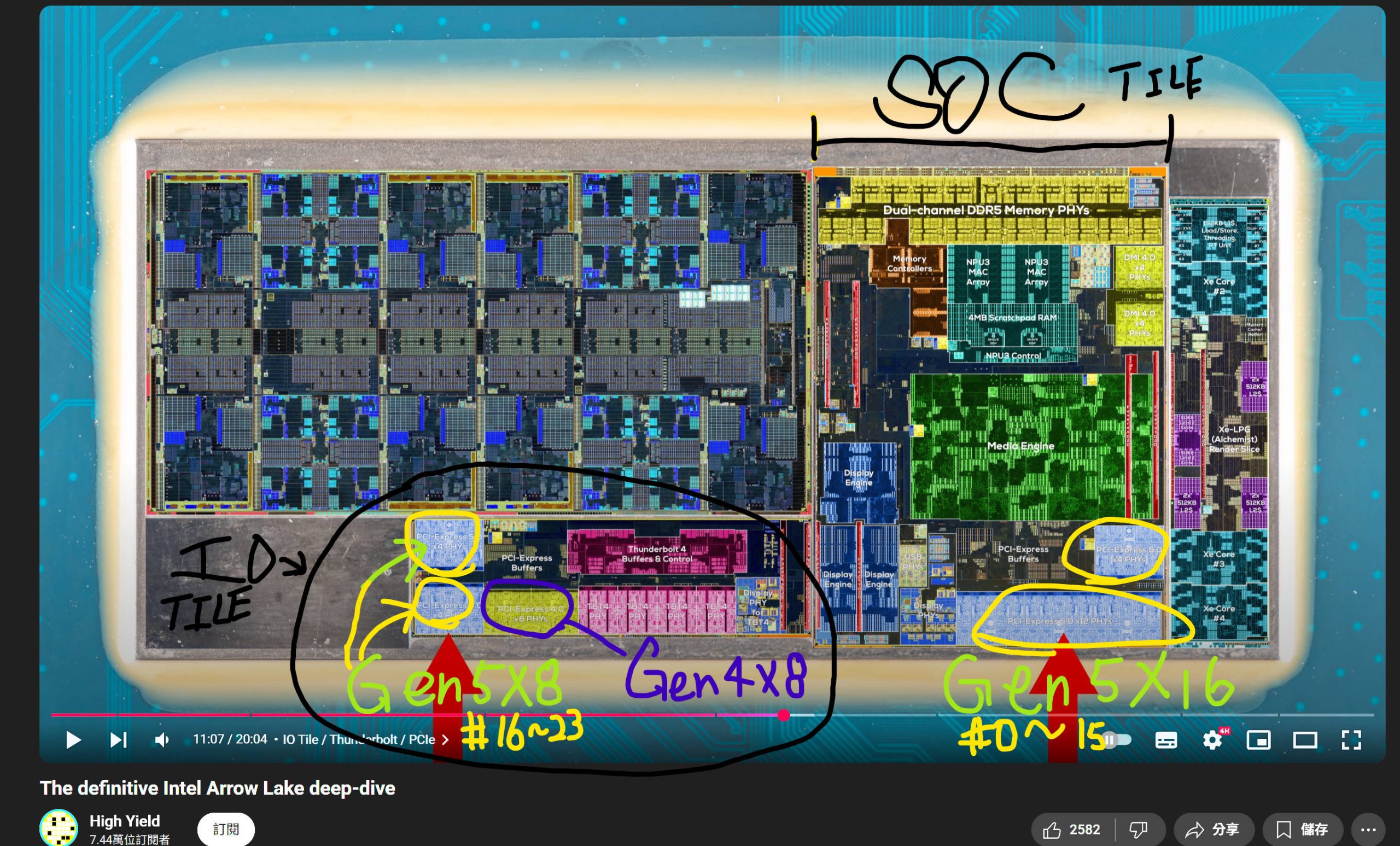

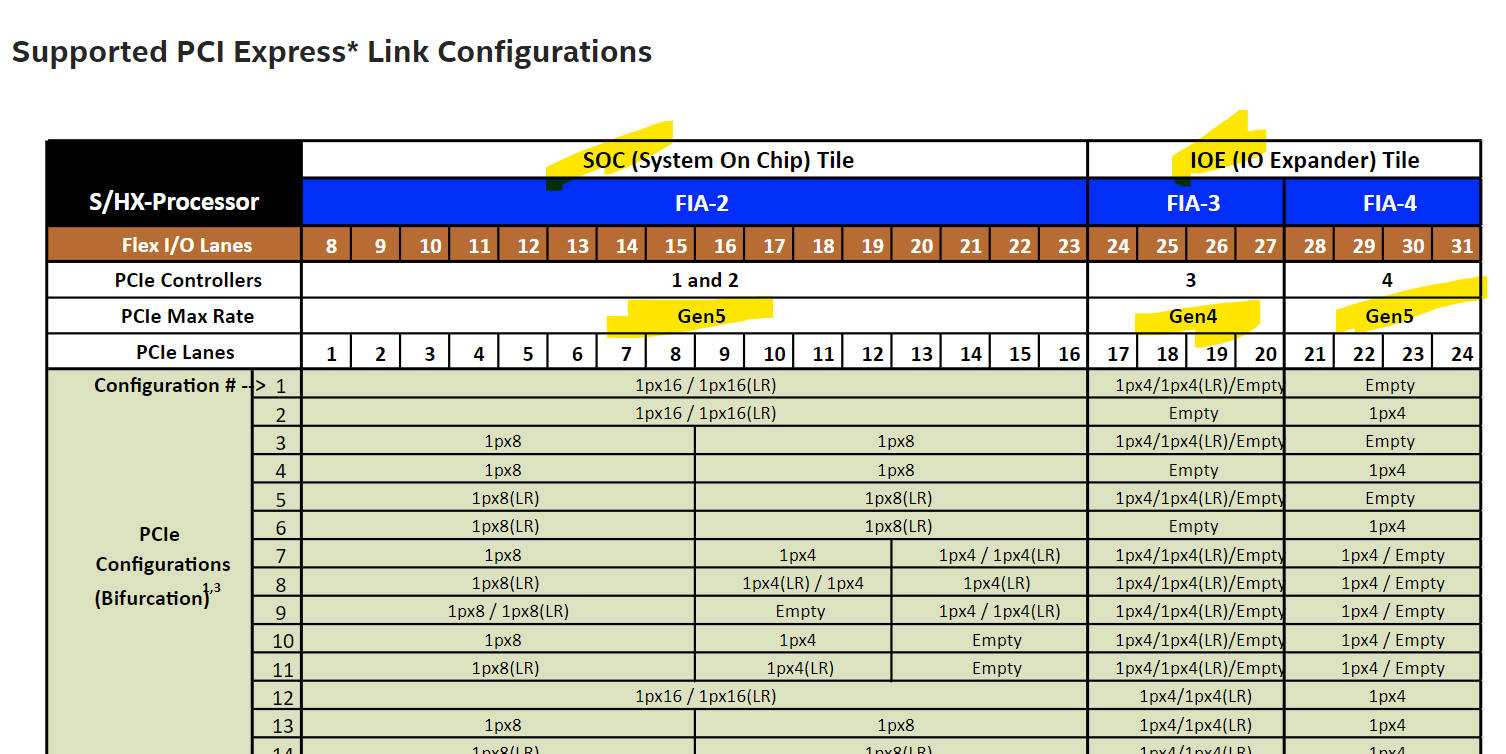

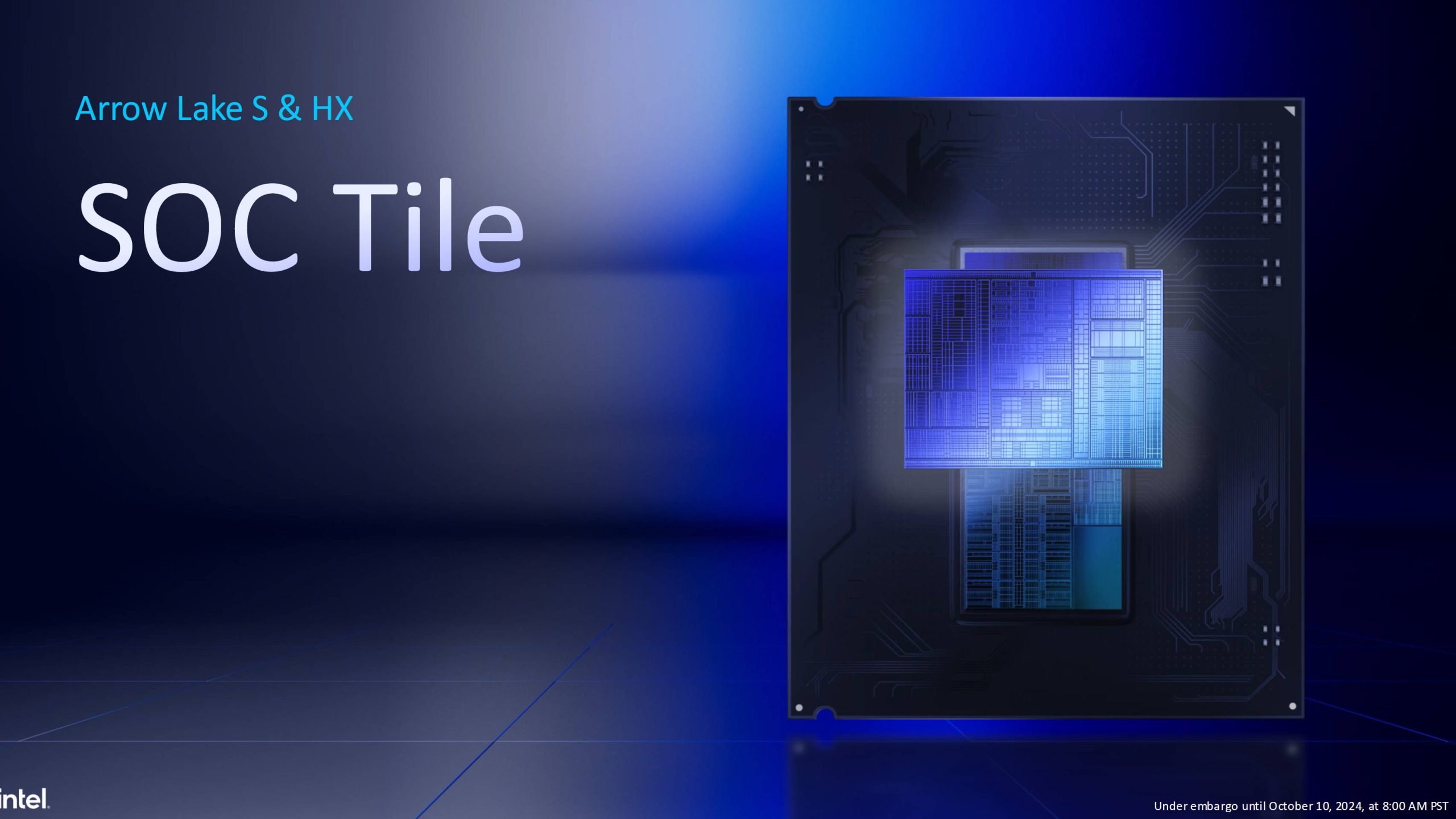

影片提到 INTEL CORE ULTRA 200S 處理器的 GEN5 通道其實共有 24 組,16 組在 SOC TILE,剩下 8 組在 IO TILE。這有別於 INTEL 給出的規格,因為 INTEL 只給出 20 組 GEN5 通道的規格 (來源)。更扯的是,HIGH YIELD 也有在 IO DIE 裡發現 GEN4 通道實際上有 8 組,不是 INTEL 所給的 4 組。這是說,如果 HIGH YIELD 的分析為真,INTEL 把 4 組 GEN5 和 4 組 GEN4 藏在 IO DIE 不給用。

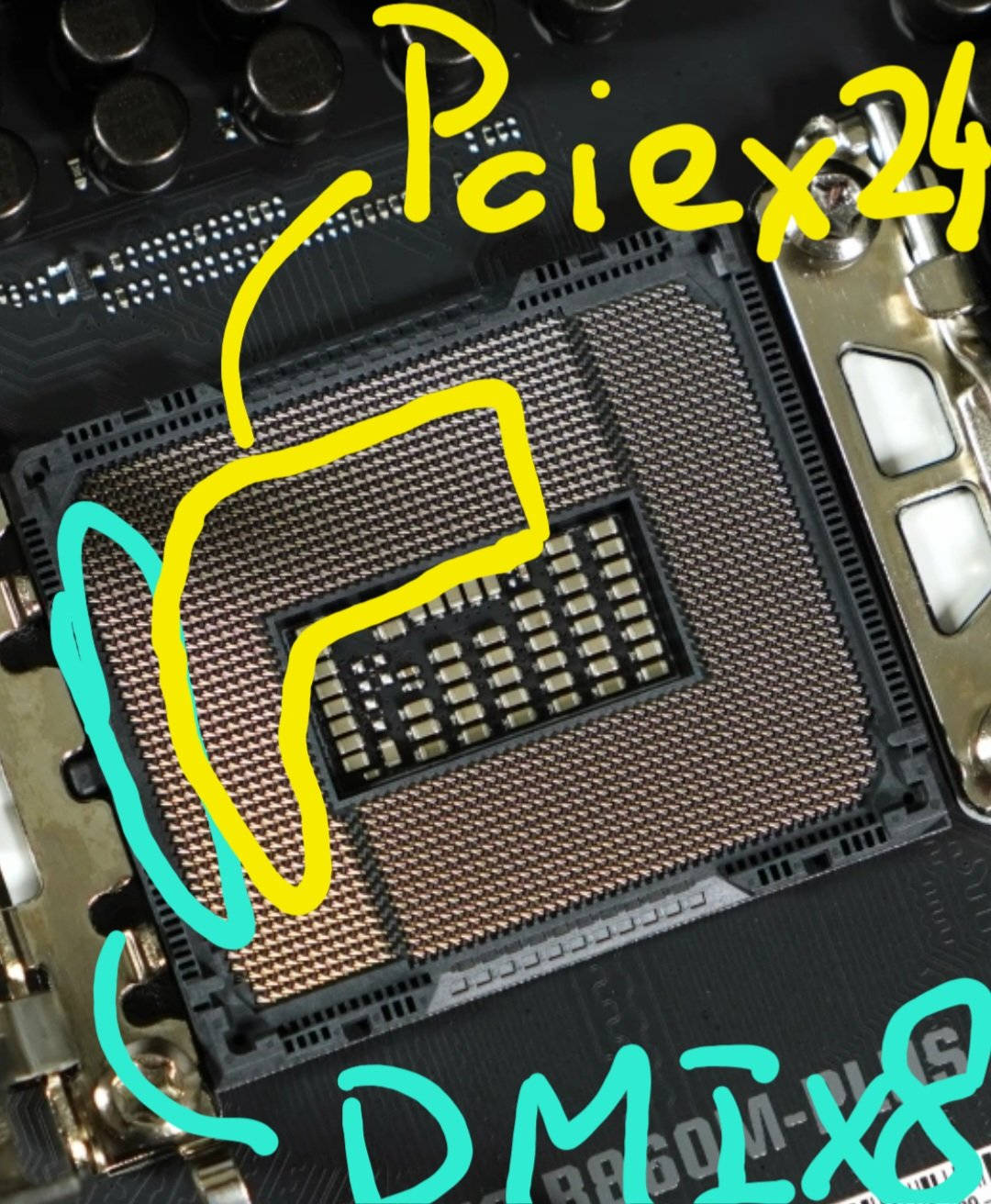

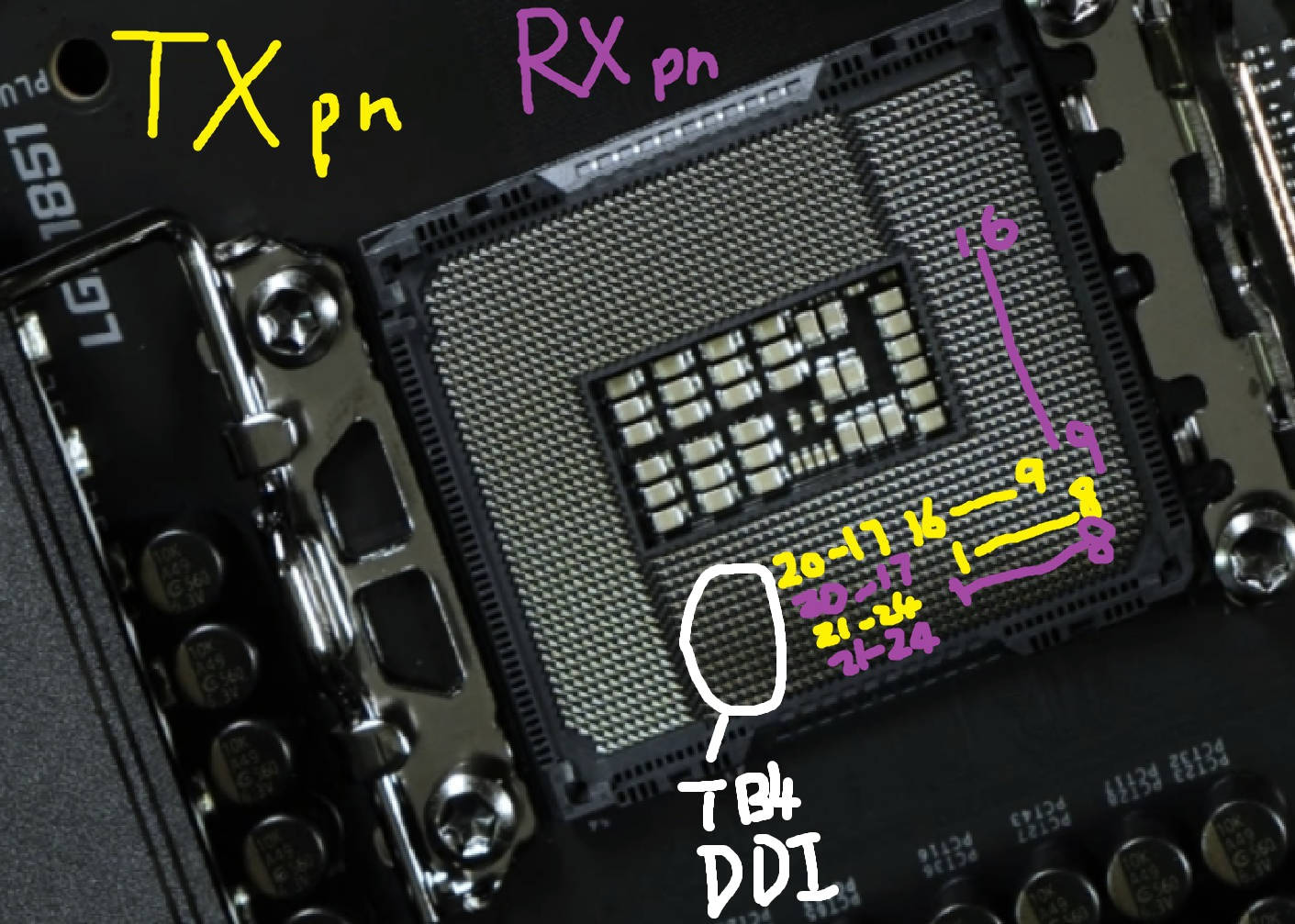

筆者翻查 LGA 1851 針腳定義,負責現有可用 PCIe 通道的針腳,就只有 24 組 ,分別是 GEN5X16 + GEN5X4 + GEN4X4。這是說,SOCKET 根本沒有多餘的 PCIe 通道針腳閒置 / 備用。LGA 1851 也有一堆針腳被定義為 RESERVED,約有 50 根,但位置上它們遠離這已知的 24 組通道的針腳,所以不似是負責那些藏於 IO DIE 未啟用的 PCIe 通道。

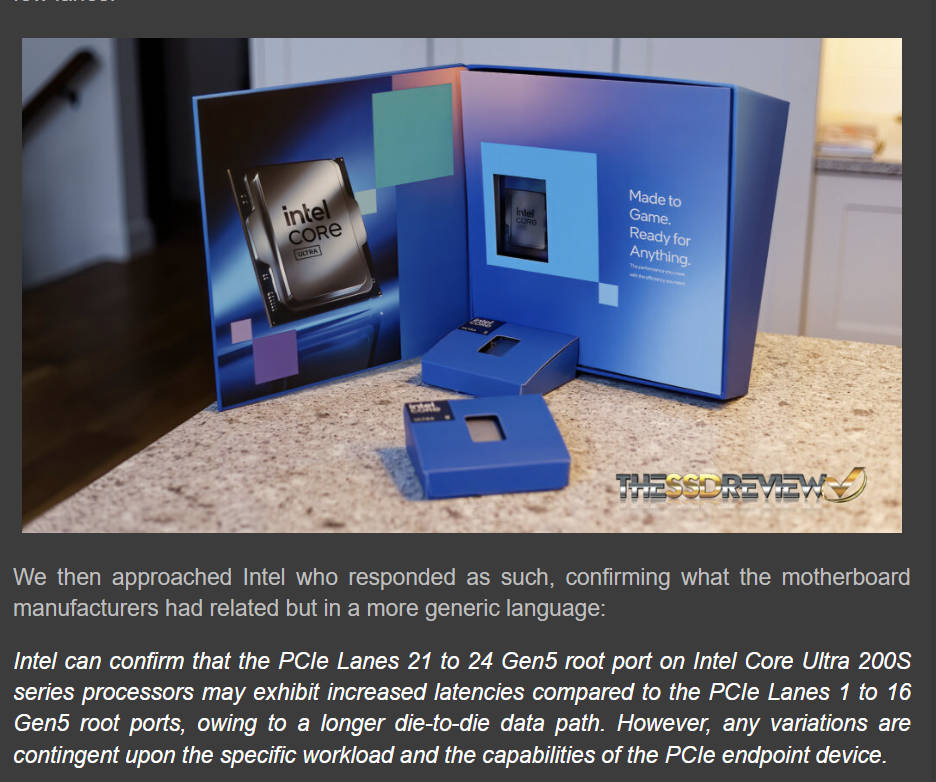

近月媒體 THESSDREVIEW (來源) 獲 ITNEL 回覆指出 CORE ULTRA 200S 處理器的 GEN5X4 通道 (非 GEN5X16 部份) 無法跑滿 GEN5 SSD 全速,大概鎖在 12000 MB/s 而非完整的速率 (約 15000 MB/s)。

Intel can confirm that the PCIe Lanes 21 to 24 Gen5 root port on Intel Core Ultra 200S series processors may exhibit increased latencies compared to the PCIe Lanes 1 to 16 Gen5 root ports, owing to a longer die-to-die data path. However, any variations are contingent upon the specific workload and the capabilities of the PCIe endpoint device. (INTEL TO THESSDREVIEW)

如果看 SOCKET 針腳,其實 17 至 20 的 GEN5 針腳就在 1 - 16 的旁邊,可惜 17 - 20 來自 IO TILE 而 1 - 16 來自 SOC TILE。筆者很好奇要是把 D2D 從預設 2.1G 超至 3.2G 甚至更高的時候,跑快一點會不會改善 LATENCIES,就算 DIE TO DIE DATA PATH 還是那麼長。由下圖可見,那些未被啟用的 GEN5X4 和 GEN4X4,其實已沒空間塞進去那邊了,上面已是供電電壓針腳。也許 LGA 1851 本來就沒打算用到它們。一組 PCIe 通道有四根針腳,可分為 RX 和 TX 兩大類,當中各自又分為正和負,所以是 TXp、TXn、RXp 和 RXn 共四根。